The hazards of electrostatic discharge (ESD) to semiconductor devices and their protection measures

I. What is static electricity?

Static electricity refers to the electric charges that are relatively stationary or changing slowly for the observer. Static electricity is an electrical energy that exists on the surface of objects; it is the result of the imbalance of positive and negative charges in a local area; it is formed through the transfer of electrons or ions. When the weather is dry, using a plastic comb to comb hair will produce a discharge sound; when taking off synthetic fiber clothes, crackling sounds will be produced, and sparks can even be seen at night. These are all common experiences of static electricity discharges that we encounter in our daily lives.

II. Hazards of Static Electricity to Semiconductor Devices

During the manufacturing, testing, storage, transportation and assembly processes of semiconductor devices, instruments, materials and operators are all prone to generating thousands or even tens of thousands of volts of static electricity voltage due to friction. When the devices come into contact with these charged objects, the charged objects will discharge through the device's pins, which may cause damage to the devices. Electrostatic discharge (ESD) poses a serious threat to semiconductor devices, especially to electrostatic-sensitive devices such as CMOS integrated circuits, MOS transistors and microwave devices. The failure modes of semiconductor device electrostatic damage mainly include:

Sudden complete failure

Sudden complete failure refers to the sudden deterioration of one or more electrical parameters of the device, resulting in the complete loss of the specified function. It is usually manifested as open circuit, short circuit, and severe drift of electrical parameters. The ESD damage of semiconductor devices mainly manifests as:

"Dielectric breakdown"

"Metalization of aluminum damage and melting"

"Local area thermal fusion of the silicon wafer"

PN junction damage and thermal-induced short circuit

"Diffusion resistance and polycrystalline resistance damage (including contact hole damage)"

"ESD can trigger the controllable silicon 'latching' effect that is inherently present within CMOS integrated circuits, resulting in the device being burned out by a large current."

(2) Potential failure

If the electrostatic potential or stored electrostatic energy of the charged body is low, or if there is a limiting resistor in the ESD circuit, a single ESD pulse is not sufficient to cause a sudden complete failure of the device. However, it will cause minor damage inside the device, and this damage is cumulative. As the number of ESD pulses increases, the threshold voltage for damage to the device gradually decreases, and the electrical parameters of the device gradually deteriorate. This type of failure is called potential failure. It reduces the device's anti-static capability and the reliability of its use. The hazard of this type of failure is much greater than that of sudden failure.

III. Typical ESD Failure Morphology of Integrated Circuits

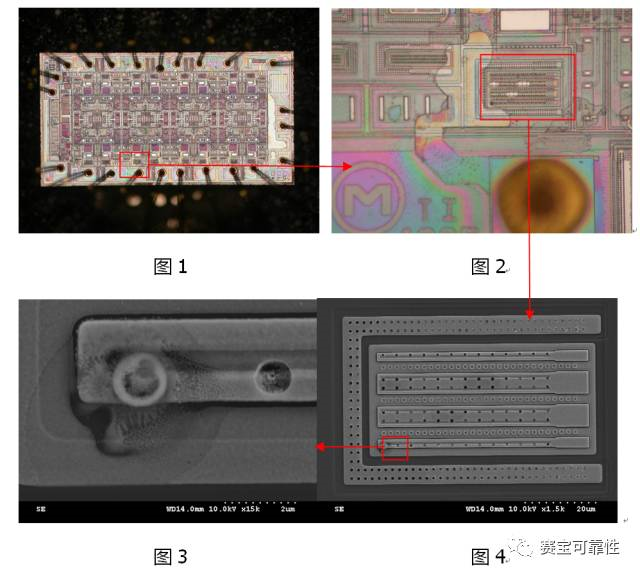

The failure mode of an eight-bit bus transceiver is manifested as no output. The test revealed that there was a resistive connection between Pin 4 and GND of the device. After removing the chip's layers, it was found that there was a significant local heat fusion in the protection network of Pin 4. The typical failure morphology is shown in Figures 1 to 4.

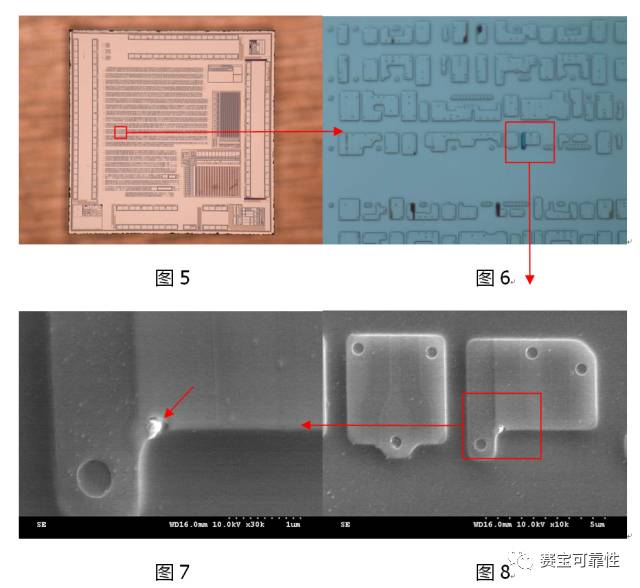

The failure mode of a keyboard control chip is manifested as abnormal response of the Shift key. Tests revealed that there was a leakage characteristic between Pin 26 and VSS of the device. After removing the chip's layers, it was found that there was a distinct breakdown morphology near Pin 25. The typical failure patterns are shown in Figures 5 to 8.

Although the ESD voltage is extremely high and the discharge can generate a large current at the moment, due to the extremely short discharge time, the total electrostatic energy is very small. From the above two cases, the damage points of the chips are all very small. This is also an important characteristic of the failure morphology of chip ESD.

Related News